## COMPUTER-AIDED DESIGN OF MONOLITHIC DISTRIBUTED AMPLIFIERS WITH YIELD OPTIMIZATION

*Man-Kuan Vai, Sheila Prasad, and Bahman Meskoob*

Department of Electrical and Computer Engineering

Northeastern University

Boston, MA 02115

### ABSTRACT

A CAD procedure for monolithic distributed amplifiers with yield optimization is presented. Considering the difficulty of fabricating exact circuit parameters with the present technology, a yield optimization, which optimizes the predicted yield rate of circuits produced when circuit elements deviate from their nominal values, has been integrated into this CAD process. Comparing a distributed amplifier designed without yield optimization and one generated with yield optimization in this procedure, the predicted yield rate has been increased from 30% to 50%.

### I. INTRODUCTION

The design of a distributed amplifier involves a careful choice of certain variables, such as the characteristics of the MESFET's, the number of stages, and the characteristics of the lines, to match with the desired frequency response. It was proposed to use a computerized optimization method in the design of monolithic MESFET distributed amplifiers [1, 2]. A design-by-simulation methodology was developed, in which the design process was transformed into a combinational optimization problem.

Despite the attractive result of achieving a virtually perfect design, a further observation reveals that the matching between the desired and simulated responses as proposed in [1, 2] is not the best measure for evaluating the design performance. In fact, it is only theoretically important to create an amplifier matching perfectly with the desired response. The monolithic fabrication of exact circuit parameters is very difficult, if not impossible, with the present technology. A design that looks good in simulation does not

guarantee a good yield rate when the statistical variations in fabrication are taken into consideration.

This article will describe how this problem is attacked by including yield optimization into the CAD process. Even though this method will be described using the design of a distributed amplifier, it can be readily applied to similar monolithic design problems.

### II. BACKGROUND

The principle of distributed amplification has existed for more than five decades. A set of references about distributed amplifiers can be found in [2].

Design procedures of distributed amplifiers based on the analysis developed in [4] for the normalized gain were described in [4-6]. These methods are manual methods which involve heavy expertise in determining a set of good initial parameters. Several repetitions are generally necessary to achieve an acceptable result.

A design-by-simulation methodology was proposed in [1, 2], in which a combinational optimization process is applied to the simulation results of a distributed amplifier represented by a set of analytical equations. A combinational optimization problem is defined as the problem of finding the minimum of a given objective function depending on many interrelated parameters. A typical objective function in this design-by-simulation method is the normalized total least squares difference between the desired and simulated characteristics.

A typical heuristic optimization process uses an iterative improvement strategy, in which an initial solution is varied and evaluated according to the objective function. Only improving solutions are accepted. One inherent drawback of this strategy is that it can be trapped into local minima of an objective function.

In the procedure described in [1, 2], a probabilistic hill-climbing algorithm, called simulated annealing [3], was used to conditionally accept some error increasing intermediate solutions. Following the concept of simulated annealing, a control parameter called pseudo-temperature was introduced into the design process. The optimization process proceeds in a way similar to traditional iterative improvement methods except that the pseudo-temperature is decreased artificially and very slowly from an initial large value. A parameter set is accepted if the objective function is reduced as in conventional methods. The acceptance of an error-increasing solution is governed by a Boltzman-like probability distribution

$$P(\Delta F, T) = e^{-k\Delta F/T},$$

where  $\Delta F$  is the difference in the objective function between the present and previous solutions,  $k$  is a weighting factor, and  $T$  is the pseudo-temperature. For the same amount of error increment, a design has a higher probability of being accepted at high  $T$ . This provides a probabilistic hill-climbing capability to escape from local minima so that a good initial solution is not necessary for a global optimization. As  $T$  is decreased gradually, the solutions will gradually concentrate into near optima and the process itself approaches into a normal iterative improvement process.

This design-by-simulation procedure has been used to design an MESFET distributed amplifier to match with a desired frequency response [1, 2]. An excellent match with the desired frequency response was demonstrated by the simulation results from an independent simulator in [2].

### III. YIELD OPTIMIZATION

The performance of a design technique formulated by an optimization process is typically evaluated by how close the product can mathematically match certain given requirements. This theoretically sound criterion of evaluating such techniques has an important flaw when it is considered more carefully. The desired requirements for a product are usually given in ranges around nominal values instead of exact values. Within the acceptable ranges, a large number of equivalent circuits can be used to match the

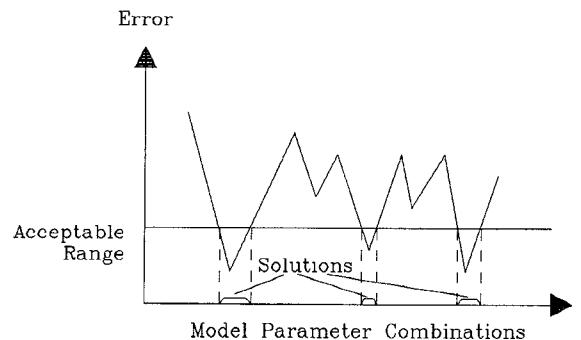

requirements. In fact, for each equivalent circuit there are an infinite number of element value combinations that give acceptable solutions. For example, different initial solutions used in an optimization process will generally give different solutions which are nevertheless equally good according to a well-defined objective function. This is demonstrated in Figure 1, which illustrates an objective function simplified into two dimensions for visibility. It is obvious that larger acceptable ranges will generate more acceptable solutions. It should be noted that any solution so generated is as good as any others including the global minimum within the acceptable requirement ranges.

Figure 1 The generation of different acceptable solutions.

In a design problem, the accuracy of the resultant elements cannot always be achieved in a physical fabrication. The best we can do is to use them as goals for fabrication. The work in this area, including [1, 2], typically provides a solution and claims its goodness by demonstrating its closeness to the desired specification. This is inadequate since if no information is provided to predict the actual performance when the parameters created in fabrication deviate from the given solution, the achievement of a good performance is not automatic. Because of the different sensitivities of the circuit characteristic on various solutions, the yield rate of a product will heavily depend on the selection of an adequate solution. The rule of thumb is to select a solution of which the desired circuit characteristics have minimum sensitivities around its neighborhood in a solution space. In other words, we need to identify a solution which will minimally affect the specification of a product when physical parameters deviate from the solution.

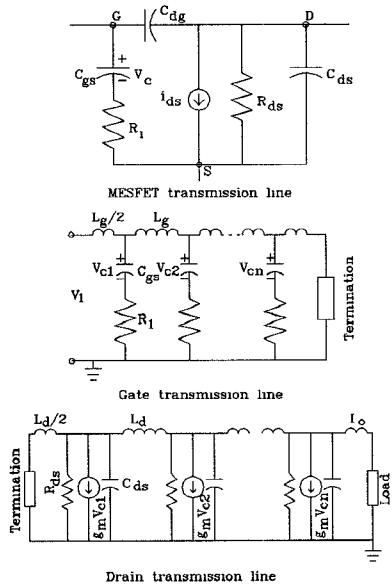

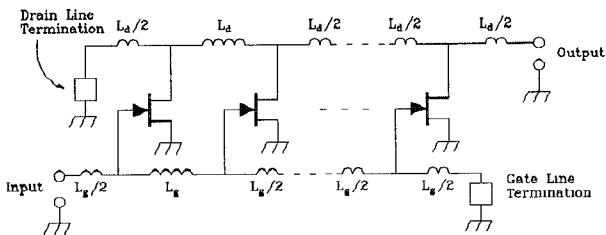

We attack this problem by including yield optimization into the CAD process. Even though we are going to describe this method using the design of a distributed amplifier, this principle can be applied to similar design problems. As originally proposed in [1], we use a circuit model, shown in Figure 2, to represent the amplifier under design which is provided in Figure 3. The gain of this amplifier was given in [4] and is used in this procedure. It is well-known that for a model configuration, there are a large number of element value combinations that give responses with acceptable errors [7]. Two sets of value combinations which generate virtually identical gain responses are given in Table 1. However, due to different gain sensitivities to different circuit elements at different values, not all these combinations will provide the same yield rate in fabrication.

Figure 2 Equivalent circuit model of a distributed amplifier.

Figure 3 Distributed amplifier under design.

Table 1 Two solutions of a distributed amplifier design.

| Parameters          | Solution W/O Yield Optimization | Solution with Yield Optimization |

|---------------------|---------------------------------|----------------------------------|

| $R_i$               | 5.17 $\Omega$                   | 6 $\Omega$                       |

| $C_{gs}$            | 0.306 pF                        | 0.234 pF                         |

| $R_{ds}$            | 256.43 $\Omega$                 | 252.83 $\Omega$                  |

| $C_{ds}$            | 0.306 pF                        | 0.234 pF                         |

| $f_c$               | 20.8 GHz                        | 27.2 GHz                         |

| $g_m$               | 0.0684 S                        | 0.0502 S                         |

| $L_d$               | 0.765 nH                        | 0.585 nH                         |

| $L_g$               | 0.765 nH                        | 0.585 nH                         |

| $n$                 | 4 stages                        | 6 stages                         |

| Response            |                                 |                                  |

| Tolerance           | $\pm 5\%$                       | $\pm 5\%$                        |

| Yield Rate          | 30%                             | 50%                              |

| Least Squares Error | <0.1                            | <0.1                             |

In a manner similar to [1], the new design process begins by minimizing an objective function which is defined using the least squares error between the simulated and desired gain responses. This is because when the frequency responses of the amplifier under design is not even close to the requirement, the yield rate can be expected to be very close to 0. It would be simply a waste of computing effort to perform yield analysis for such an intermediate result. The Boltzman-like distribution of simulated annealing described above is used to probabilistically accept error increasing intermediate results to avoid local minima.

Whenever the gain response of an intermediate solution falls within the range of acceptable amplifiers, a yield analysis is performed by a Monte Carlo process which introduces variations into circuit elements according to given fabrication parameter distributions. This yield analysis is used to simulate the deviations in circuit parameters which are unavoidable in a physical fabrication process. After the yield rate of the present design is predicted, the objective function of the simulated annealing process is also switched into one defined using the predicted yield rates. Designs with improved yield rates are accepted automatically while the acceptance of those with decreased yield rates is again determined by the Boltzman-like distribution.

This CAD procedure has been applied to the design of a monolithic MESFET distributed amplifier, of which the frequency response is given in Table 2. Table 3 describes the ranges of parameter perturbation, which are taken from a typical  $L \approx 1 \mu\text{m}$ ,  $W \approx 300 \mu\text{m}$  (nominal) MESFET fabrication process. The predicted yield rates of designs with and without yield optimization are given in Table 1. The predicted yield rate of the final solution is increased from 30% to 50% when this new method is used to take yield optimization into account.

Table 2 The desired frequency response of the amplifier under design.

| Frequency | Voltage Gain | Description    |

|-----------|--------------|----------------|

| 0.1 GHz   | 15 dB        | Flat band gain |

| 20 GHz    | 12 dB        | 3 dB point     |

Table 3 The ranges of parameter perturbation in the iterative improvement process.

| Parameters | Lower Bound       | Upper Bound       |

|------------|-------------------|-------------------|

| $R_i$      | $2 \Omega$        | $6 \Omega$        |

| $C_{gs}$   | $0.2 \text{ pF}$  | $0.7 \text{ pF}$  |

| $R_{ds}$   | $100 \Omega$      | $500 \Omega$      |

| $C_{ds}$   | $0.05 \text{ pF}$ | $0.09 \text{ pF}$ |

| $f_c$      | 20 GHz            | 32 GHz            |

| $g_m$      | 0.02 S            | 0.07 S            |

| $n$        | 1 stages          | 10 stages         |

#### IV. SUMMARY

In this paper, we have presented an improved CAD process which takes yield optimization into consideration. As demonstrated in the design example, a 66% improvement in the predicted yield rate has been achieved. The design result was simulated using TOUCHSTONE, a commercial microwave circuit simulator, and excellent results were observed. Ongoing research includes the expansion of this CAD process to also consider characteristics other than frequency response, e.g., noise figures. A physical implementation of the design solution is also under development for fabrication for verification purposes.

#### REFERENCES

- [1] Vai, M.-K., and Prasad, S., "Computer-Aided Design of MESFET Distributed Amplifier," *1989 IEEE MTT-S Digest*, pp. 565-568.

- [2] Vai, M.-K., and Prasad, S., "Computer-Aided Design of Monolithic MESFET Distributed Amplifiers," to appear in *IEEE Trans. on Microwave Theory and Techniques*, Vol. MTT-38, No. 4, April 1990.

- [3] Kirkpatrick, S., Gelatt, C. D., Jr., and Vecchi, M. P., "Optimization by Simulated Annealing," *Science*, Vol. 220, No. 4598, 13 May 1983, pp. 671-680.

- [4] Beyer, J. B., Prasad, S. N., Becker, R. C., Nordman, J. E., and Hohenwarter, G. K., "MESFET Distributed Amplifier Design Guidelines," *IEEE Trans. on Microwave Theory and Techniques*, Vol. MTT-32, No. 3, March 1984, pp. 268-275.

- [5] Becker, R. C., and Beyer, J. B., "On Gain-Bandwidth Product for Distributed Amplifiers," *IEEE Trans. on Microwave Theory and Techniques*, Vol. MTT-34, pp. 736-738, 1986.

- [6] Ross, M., and Harrison, R., "Optimization of Distributed Monolithic GaAs Amplifiers Using an Analytical/Graphical Technique," *1988 IEEE MTT-S Digest*, pp. 379-382.

- [7] Vaitkus, R., "Uncertainty in the Values of GaAs MESFET Equivalent Circuit Elements Extracted from Measured Two-Port Scattering Parameters," *IEEE 1983 Cornell Conference on High Speed Semiconductor Devices and Circuits*, pp. 301-308.